1. 플립플롭이란?

플립 플롭은 바이너리 비트를 저장하는 디지털 회로입니다. 플립 플롭에서 clock signal 는 장치의 상태를 제어합니다. 메모리 요소 또는 이진 저장 장치라고도 합니다.

이 회로는 HIGH 및 LOW의 두 가지 안정 상태를 갖습니다. 회로는 클럭 신호가 다른 상태로 변경할 수 있을 때까지 한 상태를 유지합니다. 이 회로는 쌍안정 다중 진동기라고도합니다.

플립 플롭의 output 는 이전 및 current input 에 의해서도 제어되지만 output 의 변경은 clock input 에 의해 설정된 정확한 시간에만 발생합니다.

플립 플롭은 두 가지 안정적인 상태를 가지고 있기 때문에 쌍안정 다중 진동기입니다. Low(logic 0)와 High(logic 1)는 두 가지 안정적인 상태입니다. "flip-flop"라는 용어가 사용되는 이유는 이러한 장치가 제어 신호(예: clock 또는 enable)가 적용될 때 상태 간에 전환할 수 있기 때문에 사용되며, 이는 한 상태로 "플립"하고 다른 상태로 다시 "플롭"할 수 있음을 의미합니다.

Latches는 제어 입력의 레벨 변형을 사용하여 입력 데이터를 처리합니다. 이로 인해 신뢰할 수 없는 출력이 발생합니다. 따라서 Edge 트리거가 사용됩니다.

트리거링에는 두 가지 유형이 있습니다.

- 레벨 트리거링 : 고전압 또는 저전압 구간 동안 출력이 변경될 때 발생합니다.

- 엣지 트리거링 : 신호가 하이 레벨에서 로우 레벨로 또는 로우 레벨에서 하이 레벨로 전환될 때 출력을 수정하는 장치를 에지 트리거링이라고 합니다. 포지티브 및 네거티브 엣지 트리거링은 엣지 트리거링의 두 가지 범주입니다.하강 에지(falling edge)라고도 하는 네거티브 에지(negative edge)는 에지가 높은 상태에서 낮은 상태로 전환될 때 발생합니다. 라이징 에지(rising edge)라고도 하는 포지티브 에지(positive edge)는 에지가 낮은 상태에서 높은 상태로 전환될 때 발생합니다.

2. 플립플롭의 종류

플립플롭의 종류는 다음과 같습니다.

- SR 플립플롭

- D 플립플롭

- JK 플립 플롭

- T 플립플롭

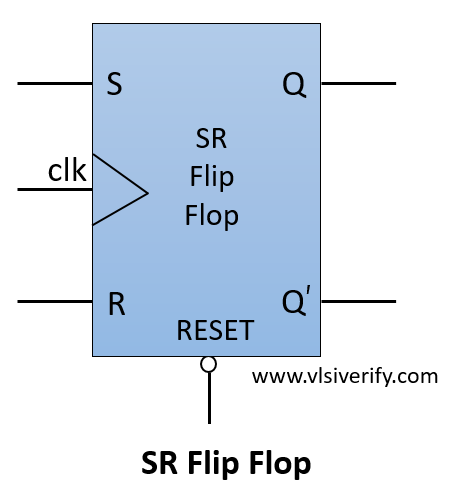

1) SR 플립플롭:

SR 플립플롭은 S와 R의 두 가지 입력이 있는 순차 회로입니다.

- S는 장치를 설정하고(즉, 출력은 1)

- R은 장치를 재설정합니다(즉, 출력은 0임).

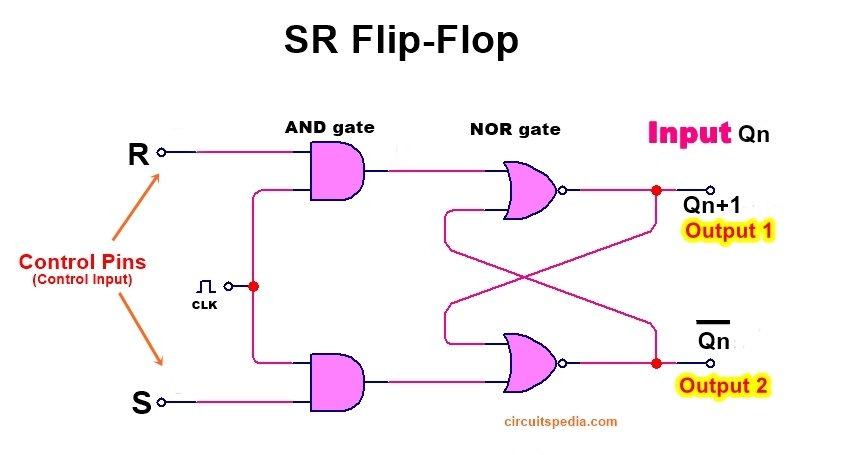

SR 플립플롭은 포지티브 클럭 전환 또는 네거티브 클럭 전환으로 작동합니다. SR 플립플롭의 회로도는 NAND 및 NOR 게이트를 사용하여 구축할 수 있습니다. SR 플립플롭의 작동은 SR Latch의 작동과 동일합니다. 플립플롭은 클록 전이가 있는 경우에만 작동하며, 클록 펄스는 활성 활성화 대신 제공됩니다.

유효하지 않은 상태는 NOR 및 NAND 게이트를 사용하는 S-R 플립플롭의 문제입니다. 이 문제는 쌍안정 SR 플립플롭을 사용하여 해결할 수 있습니다. 이 쌍안정 SR 플립플롭은 특정 잘못된 상태를 경험할 때 출력을 변경할 수 있습니다.

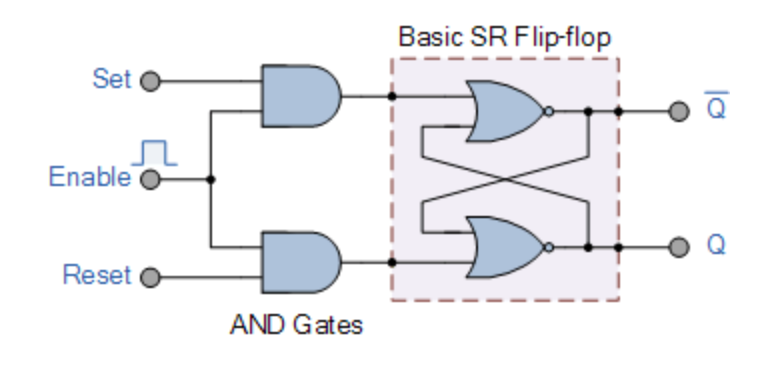

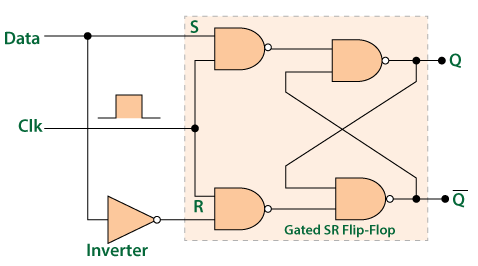

이것은 두 개의 AND 게이트를 포함하여 표준 NOR 게이트 플립 플롭을 시간이 지정된 S-R 플립 플롭으로 수정하여 수행할 수 있습니다. 이제 Gated SR Flip flop은 'S', 'R' 및 전류 출력 Q의 3개 입력으로 구성됩니다.

Gated SR 플립플롭의 회로도는 다음과 같습니다.

플립플롭은 active enable 대신 positive clock transition 가 사용되는 경우에만 작동합니다. Gated SR 플립플롭에는 세 가지 기능이 있습니다.

- 보류 상태

- 상태 설정

- 상태 재설정

AND 게이트의 입력은 클럭 펄스[CLK]를 수신합니다. AND Gates의 출력은 clock pulse의 값이 0일 때 "0"으로 유지됩니다. 펄스가 적용되면 CLK의 값이 "1"로 변경됩니다. 결과적으로 S 및 R의 값은 NOR 게이트의 플립 플롭을 통해 흐릅니다.

그러나 CLK의 HIGH 값으로 인해 S 값과 R 값의 값이 모두 "1"로 바뀔 때 둘 다 잠시 "0"으로 변경됩니다. flip flop 상태는 펄스가 사라지자마자 중간 상태로 변환됩니다. flip-flop 의 set 또는 reset input 가 두 상태 중 하나에 대해 pulse의 끝에서 "0"으로의 전환보다 "1"을 더 오래 유지하는지 여부에 따라 다릅니다. 따라서 잘못된 상태를 제거할 수 있습니다.

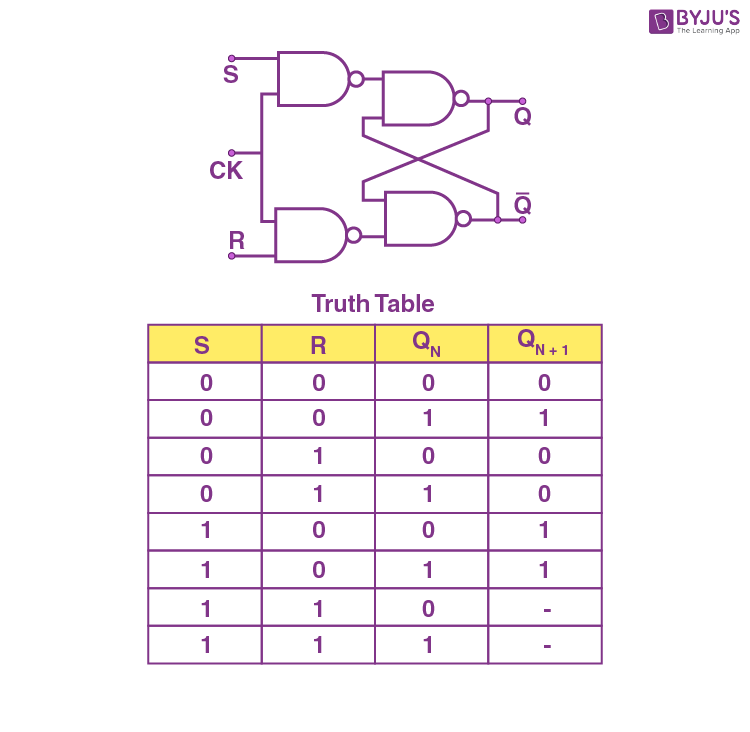

SR 플립플롭의 진리표는 다음과 같습니다. 진리표는 다양한 입력과 각각의 다음 상태 출력에 대해 Clock pulse로 분석됩니다.

- SR 플립플롭의 진리표

| CLK | S | R | Qn+1 | State |

| 0 | x | x | Qn | 변경 사항 없음 |

| 1 | 0 | 0 | Qn | 변경 없음(이전 값 유지) |

| 1 | 0 | 1 | 0 | 재설정 |

| 1 | 1 | 0 | 1 | 집합 |

| 1 | 1 | 1 | 1 | 올바르지 않음 |

- SR 플립플롭의 특성 테이블

SR 플립플롭의 특성표는 다음과 같습니다. 이 테이블은 clock pulse가 항상 높은 상태로 관찰됩니다. 특성 테이블은 특정 입력에 대한 응답으로 예정된 상태에 대한 정보를 제공합니다.

| Qn | S | R | Qn+1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | X |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | X |

- SR 플립플롭의 여기 테이블

SR 플립플롭의 여기 테이블은 현재 상태(Qn)와 다음 상태(Qn+1)에 대해 각각의 입력 S&R의 값을 나타내는 두 개의 열로 구성됩니다.

| Qn | Qn+1 | S | R |

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | X | 0 |

* NAND 게이트를 사용하는 SR 플립플롭

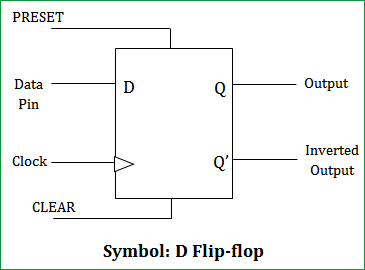

2) D 플립플롭

D 플립플롭은 clocked SR 플립플롭의 회로를 수정하여 얻어집니다. D 입력의 보수는 R 입력에 연결되고 D 입력은 S 입력에 연결됩니다.

Clock pulse 의 값이 "1"이면 D 입력이 flip flop으로 전송됩니다. clock pulse 가 높으면 flip-flop 가 활성화됩니다. 플립 플롭 출력은 D= 1일 때 1이고 출력은 D = 0일 때 0입니다. 따라서 D Flip-Flop은 Delay Flip-Flop 또는 Data Flip-Flop 또는 Transparent Flip-Flop이라고 합니다.

D Flip Flop의 그래픽 표현, 회로도, 진리표, 특성표, 여기표는 다음과 같습니다.

- D 플립플롭의 진리표:

| CP | D | Qn |

| 0 | X | Qn |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

- D 플립플롭의 특성 테이블

| Qn | D | Qn+1 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

- D 플립플롭의 여기 테이블

| Qn | Qn+1 | D |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

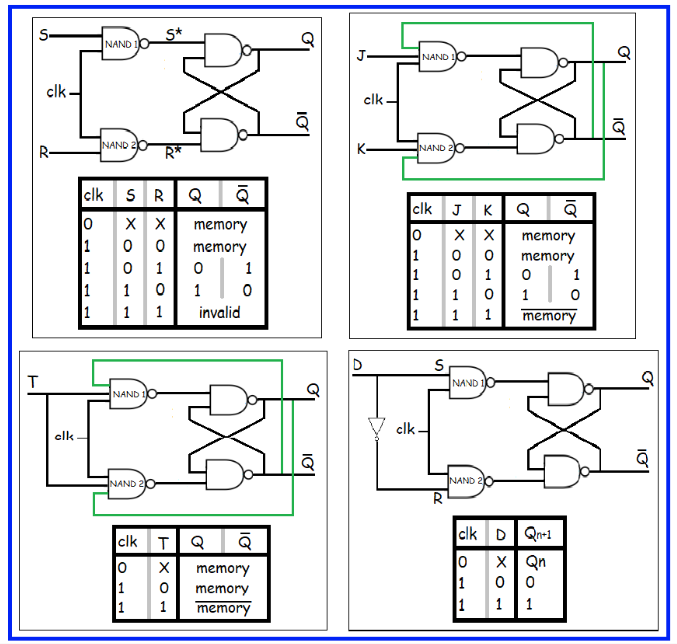

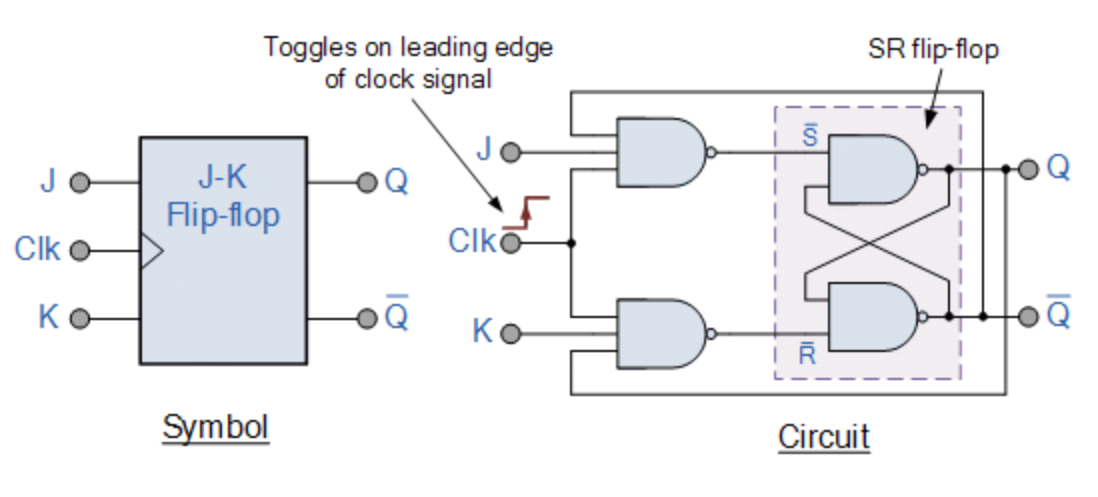

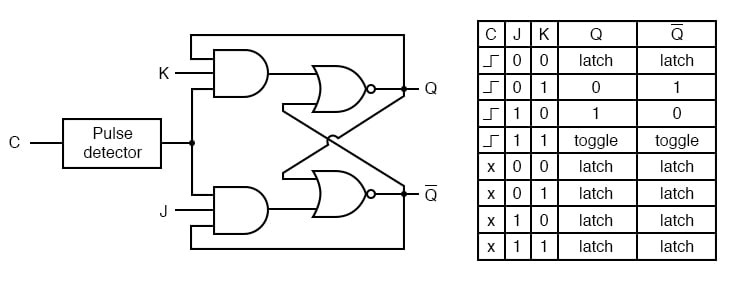

3. JK 플립플롭:

JK Flip-Flop은 SR Flip-Flop을 수정한 것으로 정의할 수 있습니다. 유일한 차이점은 S-R Flip Flop보다 중간 상태가 더 정확하고 정교하다는 것입니다.

입력 J & K는 SR 플립플롭의 SR 입력의 S&R 입력과 동일하게 동작합니다. 문자 J와 K는 각각 Set & Clear를 나타냅니다.

플립플롭은 입력 J와 K가 모두 High 상태일 때 보체 상태로 전환됩니다. 따라서 Q=1일 때 Qn+1=0, Q=0일 때 Qn+1=1로 전환됩니다.

회로에는 두 개의 3-입력 AND 게이트가 있습니다. 플립 플롭의 출력 Q는 K 및 클럭 펄스 [CP]와 같은 다른 입력과 함께 AND의 입력으로 피드백됩니다. Q 값이 1보다 먼저이면 플립 플롭은 CP 값이 "1"이면 CLEAR 신호를 수신합니다. 플립 플롭의 출력 Q'도 마찬가지로 J 및 클럭 펄스 [CP]와 같은 추가 입력과 함께 AND의 입력에 대한 피드백으로 제공됩니다. 따라서 CP 값이 1일 때 Q' 값이 이전에 1이었던 경우에만 출력이 SET가 됩니다.

JK Flip Flop의 그래픽 표현, 회로도, 진리표, 특성표, 여기표는 아래와 같습니다.

- JK Flip-Flop의 진리표

| CP | J | K | Qn+1 | State |

| 0 | x | x | Qn | 변경 사항 없음 |

| 1 | 0 | 0 | Qn | 변경 사항 없음 |

| 1 | 0 | 1 | 0 | 재설정 |

| 1 | 1 | 0 | 1 | 집합 |

| 1 | 1 | 1 | 1 | 오글 |

- JK 플립플롭의 특성표

| Qn | J | K | Qn+1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

- JK 플립플롭의 여기 테이블

| Qn | J | K | Qn+1 |

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | X |

| 1 | 0 | X | 1 |

| 1 | 1 | X | 0 |

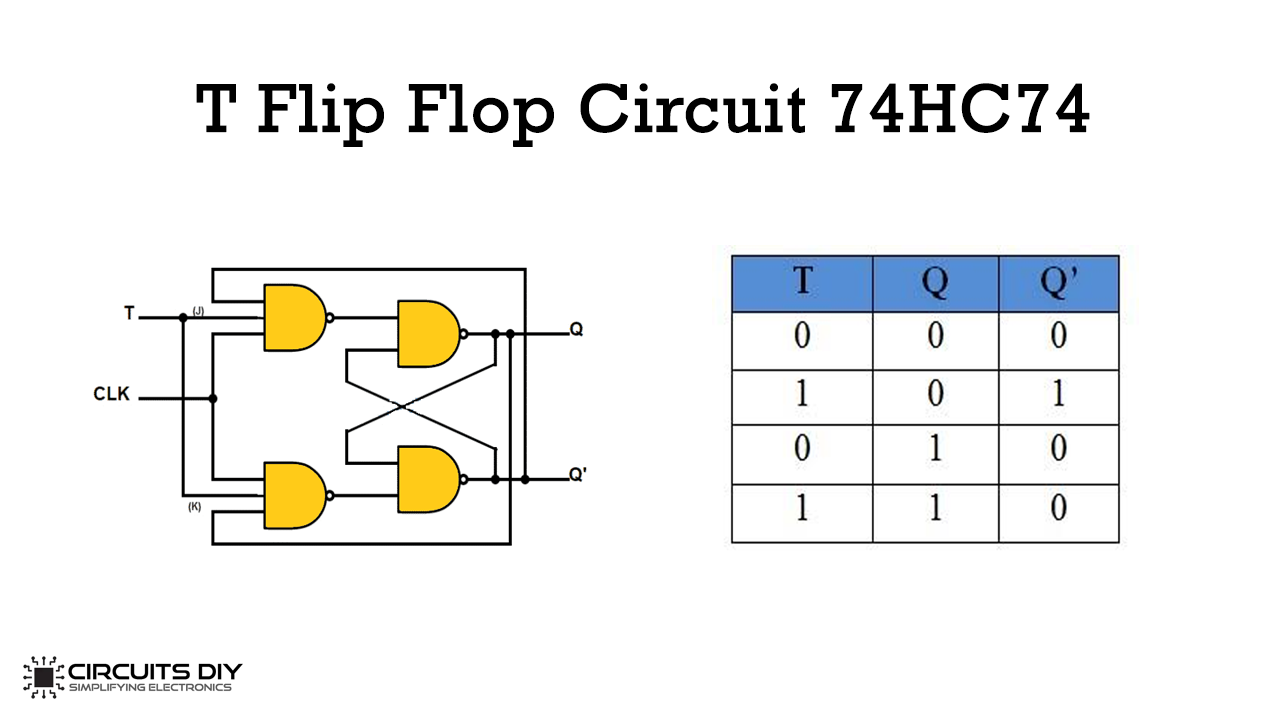

4. T 플립플롭

T 플립플롭은 J-K 플립플롭의 단순화된 형태입니다. J 및 K 입력이 결합되어 있기 때문에 이 장치는 종종 단일 입력 J-K 플립 플롭이라고 합니다. 클럭 펄스가 높으면 입력 T= 0이고 출력은 동일한 상태로 유지됩니다. 입력 T= 1이면 출력이 전환됩니다. T Flip Flop의 그래픽 표현, 회로도, 진리표, 특성표, 여자표는 다음과 같습니다.

- T 플립플롭의 진리표

| CP | T | Qn |

| 0 | X | Qn |

| 1 | 0 | 변경 사항 없음 |

| 1 | 1 | 토글 |

- T 플립플롭의 특성 테이블

| Qn | T | Qn+1 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

- T 플립플롭의 흥분 테이블

| Qn | Qn+1 | T |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

'데이터계측분석 > 전기전자 기술자료' 카테고리의 다른 글

| 퓨즈의 종류와 특성 (0) | 2024.09.03 |

|---|---|

| 회로 기판을 납땜하는 방법 (0) | 2024.09.02 |

| 필터 회로의 종류 (0) | 2024.09.02 |

| 매니폴드의 기능 및 종류 (0) | 2024.09.01 |

| LCR미터의 구성과 측정원리 (0) | 2024.09.01 |