아날로그 디지털 변환기

아날로그 디지털 변환기에 대해 알아보겠습니다.

Walt Kester의 Data Conversion Handbook에 따르면 이를 위해 1954년에 최초의 상용 ADC가 등장했습니다. 11비트 장치의 무게는 154파운드(70kg)였으며 최소 500와트의 전력을 소비하는 장치였습니다.

아날로그-디지털 변환기(ADC)는 전기적 형태의 아날로그 정보를 디지털 데이터로 변환합니다. 즉, ADC는 연속 아날로그 입력 신호를 받아 컴퓨터 또는 마이크로 컨트롤러가 사용할 수 있는 이진수로 변환합니다.

작업하게 될 아날로그-디지털 컨버터는 마이크로 컨트롤러 또는 기판의 일부로 선택되는 경우가 많지만, 특정 응용 분야에는 별도의 IC 패키지로 된 ADC를 사용할 수 있습니다.

아날로그 신호는 시간에 따라 지속적으로 변하므로 아날로그 신호를 디지털 형식으로 변환하려면 ADC가 특정 속도 또는 주파수에서 아날로그 신호를 샘플링해야 합니다.

이 비율은 나이퀴스트 정리에 의해 제어됩니다.

나이퀴스트 정리(Nyquist theorem)에 따르면 정보 손실을 방지하려면 샘플링 속도가 샘플링 중인 아날로그 신호에서 볼 것으로 예상되는 최고 주파수 성분보다 최소 두 배 이상 높아야 합니다.

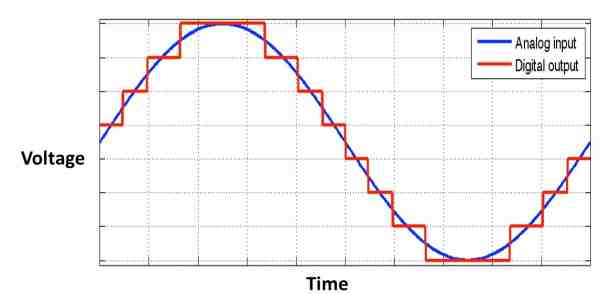

아날로그 신호 샘플링. 샘플 사이의 시간은 샘플링 기간

아날로그 신호를 수평선으로 연결하면 위와 같은 같은 계단(빨간색)이 표시됩니다. 더 많은 샘플을 채취하고 샘플링 기간을

줄이면 빨간색 신호가 더 매끄러워지고 원래 사인파처럼 보입니다.

아날로그-디지털 변환기의 종류

1) 플래시 ADC

동시 또는 병렬 아날로그-디지털 변환기라고도 하는 플래시 ADC는 주요 강점인 속도에서 이름을 따왔습니다.

플래시 방식은 기준 전압을 아날로그 입력 전압과 비교하는 비교기를 사용합니다.

아래 그림은 3비트 플래시 아날로그-디지털 컨버터의 다이어그램을 보여줍니다.

일반적인 3비트 플래시 ADC

위 회로는 저항 전압 분배기, 7개의 아날로그 비교기, 우선 순위 인코더 및 출력 래치로 구성됩니다. 전압 분배기는 총 저항이 8R이며 저항은 7개의 동일한 간격의 기준 전압은 비교기의 반전 입력에 공급됩니다.

비교기는 비반전(또는 +) 입력의 전압이 반전(또는 -) 입력의 전압보다 높으면 HIGH를 출력합니다. 반전 입력 전압이 비반전 입력 전압보다 크면 비교기 출력이 LOW가 됩니다.

아날로그 전압(Va)은 모든 비교기의 비반전 입력에 동시에 적용되므로 Va 비교기의 출력이 HIGH가 되는 특정 비교기의 기준 전압을 초과합니다.

일반적으로 플래시 ADC에는 2^n-1 가 필요합니다 비교기를 사용하여 아날로그 신호를 n비트 이진 코드로 변환할 수 있습니다. 그림에서 플래시 ADC에는 7개의 비교기만 필요하지만 대부분의 응용 제품에는 더 높은 분해능의 ADC가 필요합니다.

10비트 분해능을 가진 보다 실용적인 플래시 ADC를 원한다고 가정해 보면 1,023개의 비교기가 필요하다는 것을 알 수 있습니다. 고해상도 플래시 아날로그-디지털 컨버터를 제조하는 것은 빠르게 다루기 어렵고 비용이 많이 듭니다. 실리콘에 아날로그 회로를 장착하는 것이 항상 쉬운 것은 아니기 때문입니다. 이것은 큰 단점입니다.

2) 연속 근사 ADC

ADC 중에서 연속 근사 아날로그-디지털 변환기가 가장 인기 있는 ADC 중 하나입니다. 실제로 이러한 컨버터는 마이크로 컨트롤러에 통합되는 경우가 많습니다. 이는 이 ADC가 플래시 ADC를 제외한 다른 방법보다 변환 시간이 더 빠르기 때문일 수 있습니다. 그러나 연속 근사 변환기는 현재 알고 있는 플래시 변환기보다 실리콘(하나의 비교기 대 여러 비교기)에서 구현하기가 더 쉽습니다.

변환하고자 하는 아날로그 전압이 이진수의 잘 정의된 범위, 예를 들어 0부터 255까지라고 가정해 보면 이진 탐색은 수의 범위 중 점점 더 작은 이진수 분율을 좁힙니다. 따라서 아날로그 값이 0에서 255 사이의 이진수를 생성한다는 가정 하에 2^8 = 256 이후 8번 이상 시도하여 해당 숫자의 값을 찾을 수 있습니다.

첫 번째 근사치는 숫자가 범위의 절반에 있는지 결정합니다. 두 번째 반복은 그 절반의 절반을 찾고, 세 번째 반복은 여덟 번째 절반을 찾는 식으로 비트가 부족하여 답을 얻을 때까지 계속됩니다.

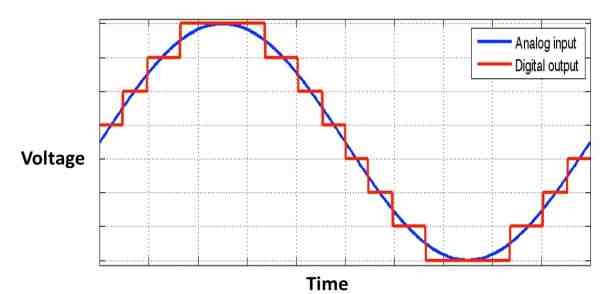

오실로스코프를 연속 근사 ADC에 연결했을 때 이와 같은 모습을 보여줍니다.

ADC 스코프 출력

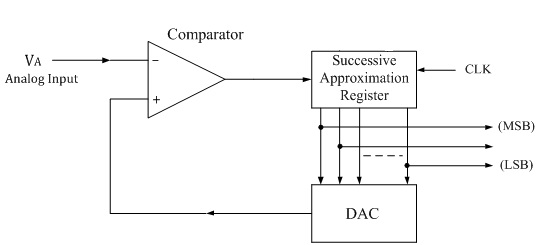

연속적인 근사 아날로그-디지털 변환기의 블록 다이어그램을 살펴보겠습니다.

연속 근사 ADC의 단순화된 제품 구성도.

먼저 DAC의 입력 비트는 최상위 비트(MSB)부터 시작하여 한 번에 하나씩 1로 설정됩니다. 각 비트가 활성화되면 비교기는 아날로그 입력 전압이 DAC의 출력보다 높거나 낮은지 여부를 나타내는 출력을 생성합니다. DAC 출력이 더 크면 비교기의 출력이 LOW가 되어 연속 근사 레지스터의 비트가 재설정됩니다(LOW 또는 0이 됨).

DAC의 출력이 아날로그 입력보다 작으면 레지스터의 비트는 1 또는 HIGH로 유지됩니다. 이 프로세스는 먼저 MSB에서 시작하여 다음으로 가장 중요한 비트, 그 다음 비트로 시작합니다. 비교기가 DAC 출력의 모든 비트(최하위 비트 또는 LSB로 끝남)를 테스트한 후 변환 주기가 완료됩니다.

3) 듀얼 슬로프 ADC

듀얼 슬로프 ADC는 종종 디지털 멀티미터, 오디오 애플리케이션 등에 사용됩니다. 이 아날로그-디지털 변환기의 이름은 적분기 출력이 시간이 지남에 따라 선형적으로 변경되고 변환 프로세스 중에 두 개의 다른 기울기가 있다는 사실에서 비롯됩니다.

적분기는 비교적 간단한 연산 증폭기 기반 회로입니다. 출력은 모든 이전 입력 값의 합계를 누적합니다. 적분기를 램프 생성기로 생각하면 됩니다.

기본 연산 증폭기 적분기.

이중 슬로프 아날로그-디지털 컨버터 제품 구성도

이상적인 연산 증폭기의 단자로 전류가 흐르지 않는다면두 단자의 전압은 동일합니다. 적분기의 양극 입력은 접지에 있기 때문에 음극 단자도 0볼트이며 이를 가상 접지라고 합니다.

전류는 연산 증폭기로 흐르지 않고 커패시터로 흘러 시간이 지남에 따라 충전됩니다. 이렇게 하면 선 또는 경사로가 만들어집니다.

변환이 시작되기 전에 자동 영점 회로는 비교기 출력을 0으로 설정합니다.

다음으로, 아날로그 입력 전압으로 인해 적분기 출력이 증가합니다. 적분기 전압이 0이 아닌 상태가 되자마자 비교기는 제어 로직을 통해 카운터를 활성화합니다.

해당 카운터가 오버플로되면 적분기 입력이 아날로그 입력 전압에서 -V로 전환됩니다 이로 인해 적분기 출력이 0(두 번째 음의 기울기)을 향해 이동합니다. 카운터는 계속 계산하고(오버플로 후 0부터 시작) 적분기 출력이 0에 도달하면 비교기가 이를 비활성화합니다.

이는 적분기 출력이 초기 단계에서 알려진 시간 동안 동작하기 때문에 작동하며 입력 전압에 비례하는 출력을 생성합니다. 두 번째 단계에서 출력은 알려진 속도로 0이 되고 첫 번째 단계의 최종 전압에 비례하는 시간에 0에 도달합니다.

듀얼 슬로프 아날로그-디지털 컨버터는 커패시터 충전 프로세스 중 클록 펄스 수를 계산하는 것을 기반으로 합니다.

T는 첫 번째 단계 동안의 시간이고 tx 는 두 번째 단계 동안의 시간을 나타냅니다.

4) 시그마-델타 ADC

블록의 최신 제품 중 하나인 시그마-델타 아날로그-디지털 변환기는 매우 높은 정확도의 변환을 자랑합니다. 또한 해당 그리스 문자에 대해 ∑-∆ ADC를 사용하며 델타-시그마 변환기라고 합니다.

시그마-델타 ADC는 최소한의 정밀 부품이 필요하기 때문에 실리콘에서 더 쉽게 실현할 수 있기 때문에 마이크로 컨트롤러에도 등장하기 시작했습니다.

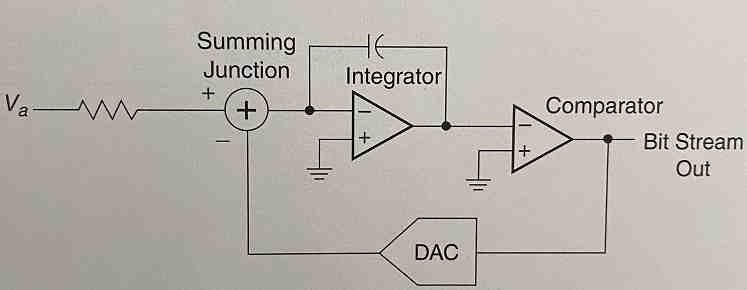

일반적인 단순화된 시그마-델타 ADC 제품 구성도는 다음과 같습니다.

일반적인 단순화된 델타-시그나 ADC 제품 구성도

시그마-델타 컨버터는 출력이 다중 비트 병렬 값이 아닌 비트의 직렬 스트림이라는 점에서 특이합니다. 그러나 이러한 특성으로 인해 병렬 컨버터(예: 플래시 ADC)로는 달성할 수 없는 최대 24비트의 매우 정확한 디지털 출력을 생성할 수 있습니다.

또한 디지털 필터링을 사용하여 잡음 수준을 매우 낮게 유지할 수 있습니다

회로는 입력 값을 적분하고 접지에 상대적인 적분기의 출력에 따라 1 또는 0을 DAC로 보내는 것으로 시작합니다. 비교기는 입력 신호가 증가한 경우 1을 생성하고 감소한 경우 0을 생성합니다.

DAC에는 +Vref 및 -Vref 두 개의 기준 전압이 있습니다. 비교기의 출력을 받아 두 레퍼런스 전압 중 하나를 합산 접합(일반적으로 차동 증폭기)으로 전환합니다. 차동 앰프는 입력 전압에서 DAC의 출력을 빼고 이를 적분기에 공급합니다.

즉, 적분기는 회로의 피드백 루프에서 DAC에 의해 도입된 이전 변경 사항을 합산합니다. 이는 특정 횟수의 반복 동안 계속되며 각 반복은 직렬 출력 스트림에 비트를 생성합니다.