오류는 수신자의 정보가 발신자의 정보와 일치하지 않을 때 발생하는 조건입니다. 전송 중에는 노이즈로 인해 송신기에서 수신기로 이동하는 디지털 신호의 이진 비트에 오류가 발생할 수 있습니다.

이는 비트가 변경될 수 있음을 의미합니다. 예를 들어 0비트가 1로 변경되거나 그 반대로 변경될 수 있습니다. 데이터 링크 계층(계층 2) 또는 전송 계층(계층 4)에서 구현된 데이터는 노이즈로 인해 스크램블될 수 있습니다. 메시지가 전송될 때 데이터가 손상될 수도 있습니다.

1. 시리얼 통신 오류 검사 방법

데이터에서 이러한 오류를 방지하기 위해 일부 추가 비트가 디지털 메시지에 추가되며 이를 오류 감지 코드라고 합니다. 오류 감지 코드는 메시지 전송 중에 발생할 수 있는 오류를 감지하는 데 도움이 됩니다.

오류 감지 방법은 일반적으로 직렬 전송의 발신자와 수신자 끝에서 수행됩니다.

2. 시리얼 통신의 오류 유형

시리얼 통신에서 발생하는 다양한 유형의 오류는 다음과 같습니다.

- 단일 비트 오류: 단일 비트 오류에서는 하나의 비트만 변경되어 데이터 단위가 잘못되거나 손상됩니다.

- 다중 비트 오류: 다중 비트 오류에서는 전송 중에 둘 이상의 비트가 변경됩니다.

- 버스트 오류: 버스트 오류에서는 전송 중에 여러 개의 연속 비트가 변경됩니다.

시리얼 통신에 대한 오류 검사를 위한 몇 가지 방법 및 알고리즘은 다음과 같습니다.

- 패리티 비트 검사

- 체크섬 오류 검사

- 순환 중복 검사(CRC)

1) 패리티 비트 검사

패리티 비트 검사는 오류 감지의 가장 간단한 형태입니다. 패리티 비트 검사에서는 오류 감지를 위해 전송된 데이터의 끝에 단일 비트가 추가됩니다. 패리티 오류 검사 방법은 오류를 감지하는 데만 사용할 수 있으며 수정할 수 없습니다.

패리티 오류 검사가 제대로 작동하려면 오류 수가 홀수여야 합니다. 오류가 많더라도 패리티 비트 합계의 변경 사항이 상쇄되기 때문입니다.

패리티 오류 검사는 홀수 또는 짝수일 수 있습니다. 패리티를 확인하기 위해 바이트의 '1'만 계산됩니다(패리티 비트 포함).

1-1) 짝수 패리티 체크

짝수 패리티 검사의 경우 1의 총 수는 짝수여야 합니다. 이 경우 패리티 비트는 0입니다. 1의 수가 홀수이면 패리티 비트는 1이고 그 반대의 경우도 마찬가지입니다.

예시:

- 1001010

이 데이터에는 3개의 1이 있습니다. 따라서 1의 수는 홀수이고 추가해야 하는 패리티 비트는 '1'이 됩니다. 따라서 데이터가 10010101됩니다.

- 1010101

이 데이터에는 4개의 1이 있습니다. 따라서 1의 수는 짝수이고 추가해야 하는 패리티 비트는 '0'이 됩니다. 따라서 데이터가 10101010됩니다.

1-2) 홀수 패리티 검사

홀수 패리티 검사의 경우 1의 총 수는 홀수여야 합니다. 이 경우 패리티 비트는 0입니다. 1의 수가 홀수이면 패리티 비트는 0이고 그 반대의 경우도 마찬가지입니다.

예시:

- 1001010

이 데이터에는 3개의 1이 있습니다. 따라서 1의 수는 홀수이고 추가해야 하는 패리티 비트는 '0'이 됩니다. 따라서 데이터가 10010100됩니다.

- 1000111

이 데이터에는 4개의 1이 있습니다. 따라서 1의 수는 짝수이고 추가해야 하는 패리티 비트는 '1'이 됩니다. 따라서 데이터가 10001111됩니다.

발신자와 수신자 측의 데이터가 패리티를 확인하고 오류를 감지합니다.

1-3) 2차원 패리티 검사

2차원 패리티 검사에서 패리티 비트는 각 행에 대해 계산됩니다. 이는 간단한 패리티 검사 비트와 동일합니다.

각 열에 대해 패리티 검사 비트를 계산해야 합니다. 그 후 두 파티 비트가 데이터와 함께 전송됩니다. 수신 측에서 두 패리티 비트는 모두 수신된 데이터에서 계산된 패리티 비트와 비교됩니다.

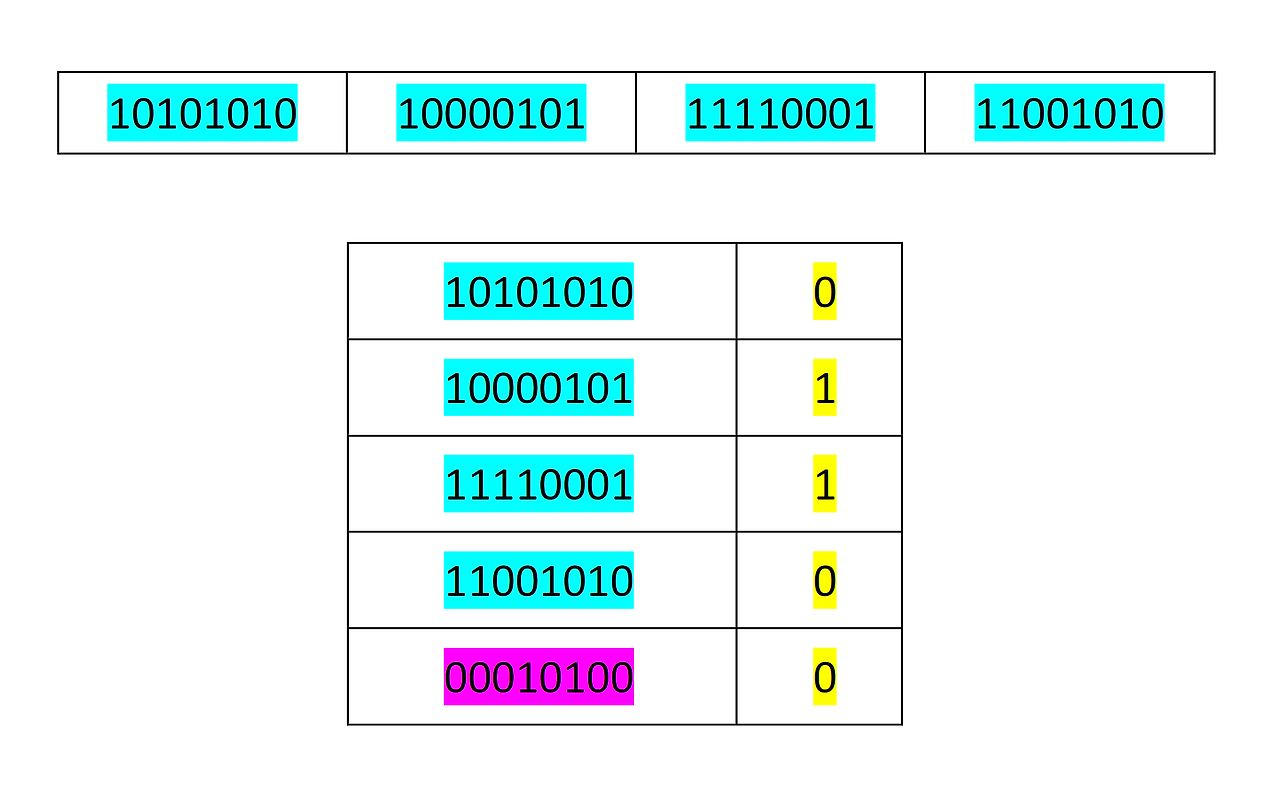

아래 예시는 짝수 패리티 검사에 대한 설명입니다.

따라서 전송할 데이터에는 열 패리티에 대한 추가 바이트가 있습니다. 전송할 최종 데이터는 다음과 같습니다.

Parity Check Error Detection 방법의 장점

- 패리티 검사 방법은 오류 감지의 가장 간단한 형태입니다.

- 패리티 검사 방법은 사용하기 쉽습니다.

- 패리티 검사 방법은 순환 중복 검사 또는 순방향 오류 수정과 같은 다른 고급 탐지 방법을 사용하여 향상시킬 수 있습니다.

Parity Check Error Detection 방법의 단점

- 단일 패리티 검사는 짝수의 비트 오류를 감지할 수 없습니다.

- 경우에 따라 패리티 검사로 인해 잘못된 오류가 발생할 수 있습니다.

- 패리티 검사는 코드의 어느 비트에 오류가 있는지 감지할 수 없습니다.

2) 체크섬(Checksum)

오류 감지의 체크섬 방법은 패리티 검사 방법에 비해 복잡합니다. 오류 감지의 체크섬 방법은 정밀도가 더 높고 오류가 누락될 가능성이 적습니다.

오류 감지 과정에서 데이터는 동일한 크기의 세그먼트로 나뉩니다. 그런 다음 송신 단위는 1의 보수 산술을 사용하여 비트를 더하여 체크섬을 만듭니다. 1의 보수에 이월 숫자가 있으면 합계에 추가됩니다.

따라서 전송된 데이터 시퀀스의 길이는 동일하게 유지됩니다. 모든 데이터가 추가된 다음 합계를 보완하여 체크섬을 만듭니다. 부울의 관점에서 보수는 모든 0을 1로 또는 그 반대로 변경하는 것을 의미합니다. 발신자 측에서 체크섬이 데이터와 함께 전송됩니다.

수신자 측에서 데이터의 합계가 수행됩니다. 그런 다음 이 합계가 체크섬에 추가됩니다. 나중에 마지막 합계의 최종 보수가 수행됩니다. 데이터에 오류가 없는 경우 결과로 생성되는 합계 보수는 항상 0입니다.

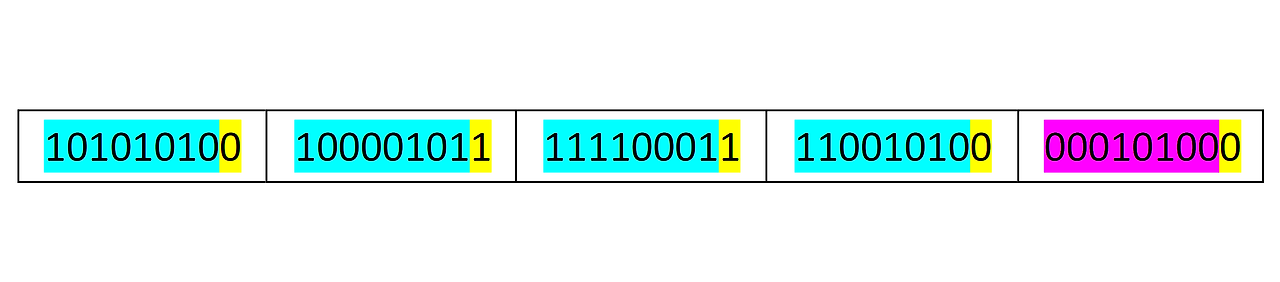

예시:

| 10101010 | 10000101 | 11110001 | 11001010 |

송신 측:

1의 보수 산술 (10101010과 10000101)을 사용하여 처음 두 세그먼트를 추가하면 결과 합계가 100101111됩니다. 그러나 여기에는 캐리가 있는 MSB 비트가 있습니다. 따라서 자릿수를 일정하게 유지하기 위해 캐리가 합계에 추가됩니다. 따라서 데이터의 처음 두 세그먼트의 최종 합계는 00110000입니다.

다음 단계에서는 처음 두 세그먼트의 합계가 세 번째 세그먼트의 데이터(예: 00110000 및 11110001)에 추가됩니다. 따라서 결과 합계는 100100001됩니다. 다시 말하지만, 캐리 비트가 있습니다. 따라서 합계에 캐리 비트를 추가하면 00100010가 됩니다.

다음 단계에서는 합계가 네 번째 세그먼트의 데이터, 즉 00100010 및 11001010에 추가됩니다. 결과 합계는 11101110입니다.

그런 다음 합계를 보완하여 체크섬을 얻어야 합니다. 따라서 여기서 체크섬은 00010001입니다.

전송된 데이터는 다음과 같습니다.

| 10101010 | 10000101 | 11110001 | 11001010 | 00010001 |

수신 측:

수신된 모든 세그먼트는 1의 보수 산술을 사용하여 추가해야 합니다. 따라서 처음 두 세그먼트인 10101010와 10000101를 더하면 합계가 100101111로 구해집니다. 여기에도 캐리 비트를 추가하여 00110000을 얻습니다.

다음 단계에서는 처음 두 세그먼트의 합계가 세 번째 세그먼트의 데이터(예: 00110000 및 11110001)에 추가됩니다. 따라서 결과 합계는 100100001됩니다. 다시 말하지만, 캐리 비트가 있습니다. 따라서 합계에 캐리 비트를 추가하면 00100010가 됩니다.

다음 단계에서는 합계가 네 번째 세그먼트의 데이터, 즉 00100010 및 11001010에 추가됩니다. 결과 합계는 11101110입니다. 그리고 합계가 다섯 번째 세그먼트의 데이터, 즉 11101110 및 00010001에 추가됩니다. 결과 합계는 11111111입니다.

합계의 보수는 00000000이 됩니다. 따라서 수신된 데이터에는 오류가 없습니다.

Checksum Error Detection 방법의 장점

- 오류 감지의 체크섬 방법은 구현하기 쉽습니다.

- 체크섬 코드는 매우 빠르게 계산할 수 있으므로 실시간 데이터 패킷 전송에 적합합니다.

- 오류 감지의 체크섬 방법은 대기 시간이 매우 짧습니다.

Checksum Error Detection 방법의 단점

- 오류 감지의 체크섬 방법은 일반적인 오류만 감지할 수 있습니다.

- 오류 감지의 체크섬 방법은 오류만 감지할 수 있습니다. 그것은 그것들을 바로잡을 수 없습니다.

- 세그먼트의 하나 이상의 비트가 손상되면 두 번째 세그먼트에 있는 반대 값의 해당 비트도 손상됩니다.

3) 순환 중복 검사(CRC)

오류 감지의 순환 중복 검사 방법은 다항식 나눗셈을 사용합니다. 오류 감지의 순환 중복 검사 방법은 1과 0의 수를 확인하는 것뿐만 아니라 순서가 올바른지 여부도 확인합니다.

순환 중복 검사 방법에서는 검사할 데이터를 다항식 방정식처럼 취급합니다. 그런 다음 방정식을 선택한 제수로 나눕니다. 제수의 값은 순환 중복 검사의 정확성과 유용성을 결정하는 데 필수적입니다.

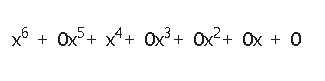

이진 정보는 검사방법에 맞게 다항식 방정식으로 변환해야 합니다. 이를 위해 이진수는 다항식 표현식의 계수가 됩니다. 다항식 표현식의 길이는 나눌 코드의 길이와 일치합니다.

CRC에서는 중복 비트 시퀀스가 데이터 단위의 끝에 추가됩니다. 이중화 비트의 시퀀스를 순환 중복 검사 비트(cyclic redundancy check bits)라고 합니다. 이러한 비트를 추가하면 결과 데이터는 미리 결정된 이진수로 정확하게 나눌 수 있게 됩니다.

수신기 측에서 데이터는 동일한 숫자로 나뉩니다. 나머지가 0이면 데이터가 올바른 것으로 간주되고 수락됩니다.

나머지가 0이 아닌 경우 데이터가 손상되어 거부해야 함을 나타냅니다.

예시:

데이터가 1010000이라고 가정해 보겠습니다.

다항식은 다음과 같습니다.

다른 다항식 또는 방정식을 나눌 키가 1001이라고 가정해 보겠습니다. 따라서 방정식은 다음과 같습니다.

이제 나눗셈이 수행되고 나머지가 발견됩니다. 그런 다음 나머지는 전송할 데이터에 추가됩니다. 나눗셈은 XOR 나눗셈을 사용하여 수행됩니다.

수신된 데이터도 키로 나뉩니다. 수신자 측의 나머지와 송신자 측의 나머지 값의 차이가 0이면 데이터가 손상되지 않습니다. 차이가 0이 아닌 경우 전송되는 데이터에 손상이 있습니다.

'데이터계측분석 > 데이터통신 기술자료' 카테고리의 다른 글

| 디바이스넷 기능과 사양 (0) | 2024.08.13 |

|---|---|

| 모드버스 아스키와 RTU 데이터 프레임 구성 (0) | 2024.07.28 |

| TCP와 UDP의 개요와 차이점 (0) | 2024.07.24 |

| 인터넷 프로토콜(IP)의 기초 (0) | 2024.07.24 |

| RS-232와 RS-485의 차이점 (0) | 2024.07.20 |