텍사스 인스트루먼트(Texas Instruments)의 잭 킬비(Jack Kilby)가 세계 최초의 집적 회로(IC) 칩을 전자 산업에 도입한 것은 1958년이었습니다. 이 발명은 IC가 당시 사용 된 기존 회로에 비해 더 안정적이고 컴팩트하며 전력을 절약 할 수 있었기 때문에 들불처럼 퍼졌습니다. 곧 이것은 들불처럼 퍼졌고 모든 회사는 오늘날 우리가 알고 있는 현대 전자 제품으로 이어지는 집적 회로를 제작하고 적용하기 시작했습니다.

IC 제조에는 많은 제조 기술이 사용되며, 가장 인기 있는 두 가지 유형은 1963년에 도입된 TTL(Transistor Transistor Logic)과 1968년에 도입된 CMOS(Complementry Metal Oxide Semiconductor)입니다.

1. CMOS란?

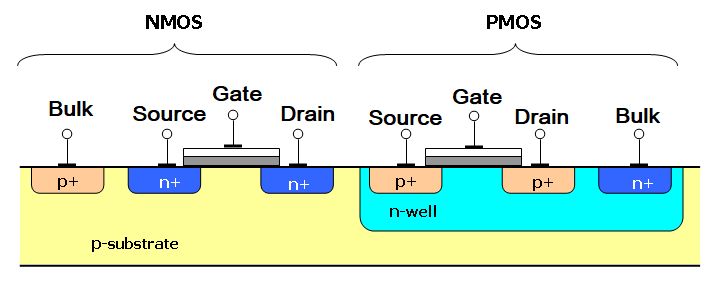

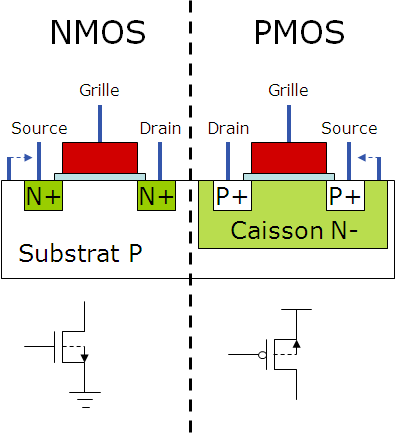

CMOS는 Complementary Metal Oxide Semiconductor의 약자로 다양한 응용 분야에서 사용되는 IC를 제조하는 기술입니다. CMOS는 가장 일반적인 MOSFET 제조 유형으로, logic functions를 수행하기 위해 p형 및 n형 금속 산화물 전계 효과 트랜지스터의 상보적이고 대칭적인 쌍을 사용합니다. 단일 패키지에서 활용되는 PMOS와 NMOS 트랜지스터의 조합은 다음과 같습니다.

다양한 유형의 집적 회로는 마이크로 프로세서, 마이크로 컨트롤러, 메모리 칩 및 기타 여러 디지털 논리 회로와 같은 CMOS 기술을 사용하여 구성됩니다. 데이터 변환기, 이미지 센서 및 트랜시버와 같은 정적 아날로그 회로에서 이 기술은 널리 사용됩니다. CMOS는 하이와 로우 또는 0과 1의 두 로직을 모두 전파합니다.

2. TTL이란?

TTL은 Transistor-Transistor Logic의 약자입니다. 바이폴라 접합 트랜지스터(BJT)로 구성된 로직 제품군입니다. 여기서 두 기능(logic 및 amplifying)은 모두 트랜지스터에 의해 수행됩니다. 따라서 Transistor-Transistor Logic이라고 합니다.

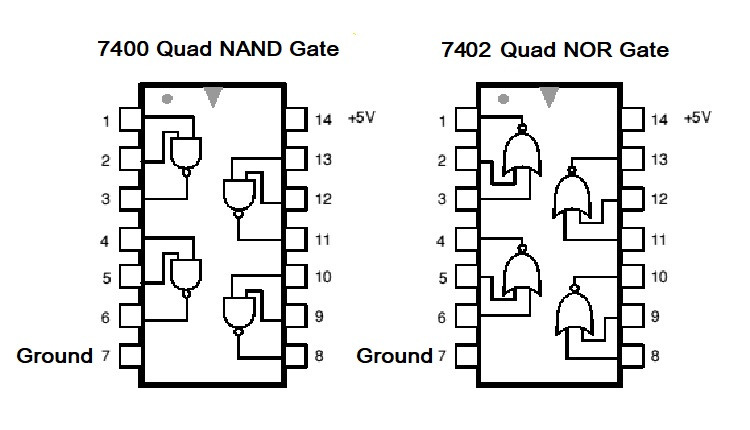

TTL 로직 IC의 이상적인 예로는 7400 NAND 또는 7402 NOR 게이트와 같은 로직 게이트 IC가 있습니다.

TTL은 트랜지스터-트랜지스터 로직의 약어입니다. TTL 로직은 여러 이미터와 여러 입력이 있는 여러 트랜지스터를 사용합니다. 트랜지스터-트랜지스터 로직의 유형은 표준 트랜지스터-트랜지스터 로직, 고속 트랜지스터-트랜지스터 로직, 쇼트키 트랜지스터-트랜지스터 로지c, 고전력 트랜지스터-트랜지스터 로직, 저전력 트랜지스터-트랜지스터 로직 및 고급 쇼트키 트랜지스터-트랜지스터 로직입니다.

TTL 로직 게이트는 바이폴라 접합 트랜지스터와 저항으로 구성됩니다. 우주 응용 분야를 위한 방사선 강화 TTL 패키지, 속도와 더 적은 전력 소비의 탁월한 조합을 제공할 수 있는 저전력 쇼트키 다이오드와 같이 다양한 특정 목적을 위해 개발된 TTL의 많은 변형 이 있습니다.

3. CMOS와 TTL의 차이점

TTL 칩에 비해 CMOS의 장점은 CMOS가 동일한 재료 내에서 더 높은 밀도의 로직 게이트를 갖는다는 것입니다. TTL 칩은 유휴 상태에서도 CMOS 칩이 소비하는 전력에 비해 더 많은 전력을 소비합니다. CMOS의 전력 소비는 다양한 요인에 따라 달라지며 가변적입니다. 클럭 속도는 전력 소비의 주요 요인 중 하나입니다. 클럭 값이 높을수록 전력 소비가 높아집니다. 비교를 할 때 CMOS 칩의 단일 게이트는 10nW의 전력을 소비하는 반면 TTL 칩의 동등한 게이트는 약 10mW의 전력을 소비합니다. 그 차이는 상당히 높기 때문에 CMOS 칩이 항상 TTL 칩보다 선호됩니다.

설계 및 제작을 고려할 때 CMOS 칩은 매우 섬세하고 정전기 방전에 매우 취약하기 때문에 다루기 어렵다는 것은 의심의 여지가 없습니다. 아주 미세한 양의 정전기는 CMOS 칩에 손상을 줄 수 있습니다. 따라서 사람들은 종종 CMOS의 단자를 만지는 것만으로도 원치 않게 칩을 손상시킵니다.

CMOS와 TTL의 몇 가지 기본적인 차이점은 다음과 같습니다.

- CMOS 구성 요소는 일반적으로 TTL 구성 요소와 비교할 때 더 비쌉니다. 그러나 시스템 수준에서 CMOS 칩은 TTL 칩에 비해 크기가 작기 때문에 저렴합니다.

- 둘 다에 전파 지연이 있습니다. 평균적으로 TTL의 전파 지연은 일반적으로 10nS인 반면 CMOS의 전파 지연은 20에서 50nS 사이입니다

- CMOS는 상승 및 하강 시간이 길기 때문에 CMOS 칩을 사용하면 디지털 신호가 더 간단하고 저렴합니다.

- 둘 다의 전압 레벨 범위에는 상당한 차이가 있습니다. TTL의 경우 4.75V에서 5.25V까지이며 CMOS의 경우 낮은 레벨에서 0에서 1/3 VDD까지, 높은 레벨에서 2/3VDD에서 VDD 사이입니다.

- CMOS 기술은 TTL 로직에 비해 더 경제적이고 선호됩니다.

- CMOS의 전류 요구 사항이 낮기 때문에 전력 소비가 제한됩니다. 따라서 최상의 전력 관리로 회로를 설계하는 것이 더 쉽습니다.

- 전자기 파괴 CMOS 구성 요소는 TTL 구성 요소에 비해 더 민감합니다

- CMOS는 TTL에 비해 전송 중 노이즈를 줄일 수 있다는 또 다른 장점이 있습니다

- 정상 작동, 즉 팬아웃에서 게이트의 출력에 연결할 수 있는 표준 부하의 수는 TTL의 경우 10인 반면 CMOS의 경우 50입니다.

- 게이트에 연결할 수 있는 표준 입력의 수는 팬 인이며, TTL의 경우 약 12-14이고 CMOS의 경우 10입니다.

- CMOS 회로는 TTL 회로보다 노이즈 내성이 우수합니다.

- TTL 구성에 사용되는 기본 게이트는 NAND 게이트이며 NAND-NOR 게이트는 모두 CMOS 회로에 사용됩니다.

TTL 및 CMOS 로직 제품군을 비교하면 CMOS는 TTL 구성 요소보다 더 많은 이점이 있습니다. TTL보다 전력 소비가 적고 경제적입니다. CMOS의 출력 전력은 더 높고 크기도 더 작습니다. 소음에 대한 내성이 높기 때문에 더 낮은 수준의 소음이 전송되는 동안 싱글이 전송됩니다. 또한 전파 지연이 더 작기 때문에 TTL 회로가 회로하는 신호를 더 빠르게 전송할 수 있습니다. 팬이 수보다 많을수록 CMOS 회로의 출력 단자에 부하 수를 연결할 수 있습니다.

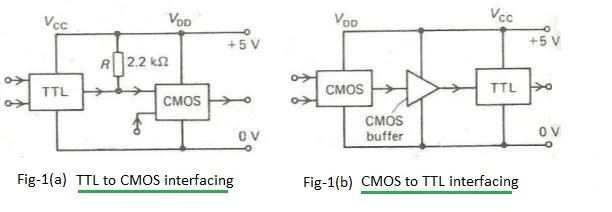

CMOS는 FET로 구성되고 TTL 회로는 BJT로 구성되기 때문에 CMOS 칩은 훨씬 빠르고 효율적입니다. TTL에 비해 CMOS의 단일 칩에서 훨씬 더 높은 밀도의 논리 기능이 있습니다. 또한TTL 회로의 전력 소비는 CMOS의 전력 소비와 비교할 때 더 높습니다. CMOS는 전력 소비가 적지만 CMOS 칩은 정전기 방전에 더 취약하므로 쉽게 손상될 수 있습니다. CMOS 칩은 TTL 로직을 가질 수 있으며 TTL IC의 대체에 사용될 수 있습니다.

'데이터계측분석 > 전기전자 기술자료' 카테고리의 다른 글

| RFID모듈의 구성과 종류 (1) | 2024.09.09 |

|---|---|

| 배터리의 종류와 특징 (0) | 2024.09.09 |

| 전자부품의 기호 (0) | 2024.09.08 |

| 광커플러의 구성과 응용 (0) | 2024.09.08 |

| AC커플링과 DC커플링의 이해 (0) | 2024.09.07 |