SPI 버스 개요

SPI 직렬 버스는 원래 모토로라에 의해 설립되었습니다. 오늘날, 이 제품은 집적 회로 제조업체에서 장치 대 프로세서 또는 FPGA 제어를 위해 사용하는 가장 일반적인 통신 버스 중 하나입니다.

예를 들어 ADC, DAC, 센서 및 기판 전용 제품이 있습니다. IEEE 또는 다른 조직에서 표준으로 규제하지는 않지만 대부분의 장치는 이 문서에 설명된 공통 규칙 집합을 준수합니다.

SPI는 전이중으로 작동하는 동기식 직렬 데이터 링크입니다. 즉, 데이터를 전달하는 신호는 동시에 양방향으로 이동합니다. 장치는 마스터가 데이터 프레임을 시작하는 마스터/슬레이브 프로토콜을 사용하여 통신합니다.

마스터가 클록을 생성한 후 슬레이브 장치를 선택하면 데이터가 동시에 한쪽 또는 양쪽 방향으로 전송될 수 있습니다. 수신된 바이트가 의미가 있는지 여부를 아는 것은 마스터 및 슬레이브 장치에 달려 있습니다.

이를 위해서는 장치가 "전송 전용" 프레임에서 수신된 바이트를 폐기하거나 "수신 전용" 프레임에 대한 더미 바이트를 생성해야 할 수 있습니다.

네 가지 일반적인 SPI 신호는 다음과 같습니다.

- 클럭(SCLK) - 이 신호는 마스터에 의해 생성됩니다. 전송의 다른 신호는 이 클럭의 에지 타이밍에 따라 변경됩니다.

- 마스터 데이터 출력, 슬레이브 데이터 입력(MOSI) - 이 라인은 마스터에서 슬레이브로의 출력입니다. 마스터 클럭 에지와 동기화된 비트 단위로 전송합니다.

- 마스터 데이터 입력, 슬레이브 데이터 출력(MISO) - 이 라인은 연결된 모든 슬레이브의 출력입니다. 마스터 클럭 에지와 동기화된 슬레이브에서 비트 단위로 전송합니다.

- 칩 선택(CS) 또는 슬레이브 선택(SS) - 각 라인이 시스템의 개별 슬레이브로 이동하는 신호 뱅크입니다. 해당 슬레이브와 통신할 수 있도록 한 번에 한 줄이 어설션됩니다. 칩 선택은 일반적으로 낮게 어설션됩니다.

그림 1: 하나의 슬레이브에 연결된 마스터

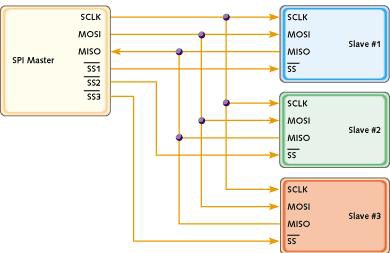

그림 2: 여러 슬레이브에 연결된 마스터 개별 슬레이브에 연결된 뱅크 오브 칩 선택 라인이 한 번에 하나씩 통신할 수 있도록 합니다.

기본 단계별 전송

- 마스터는 특정 SS 라인을 로우로 구동하여 해당 슬레이브와의 통신을 시작합니다.

- 선택한 SS가 로우가 되면 SCLK의 한쪽 에지(상승 또는 하강)가 장치(마스터 및 슬레이브)에 신호를 보내 MOSI 및 MISO를 전송 중인 올바른 데이터 비트로 전환합니다.

- SCLK 라인의 다른 가장자리(상승 또는 하강)는 MOSI 및 MISO에 비트를 등록하도록 디바이스에 신호를 보내 비트를 디바이스로 효과적으로 읽습니다.

- 전송은 장치가 지정된 비트 수(일반적으로 8,16 또는 32)를 교환할 때까지 이러한 방식으로 계속됩니다.

- 전송이 완료된 후 마스터는 슬레이브의 SS 라인을 다시 하이로 풀링하고 네트워크의 다른 슬레이브로 이동하거나 해당 SS 라인을 다시 로우로 당겨 동일한 슬레이브로 전송을 다시 시작합니다.

그림 3: 기본 SPI 전송의 상태 차트

SPI 프로토콜의 매개 변수

클록 극성(CPOL) 및 클록 위상(CPHA)이라고 하는 파라미터는 데이터가 구동되는 클록 신호의 에지를 결정합니다. 이 두 매개 변수에는 두 가지 가능한 상태가 있으므로 네 가지 가능한 조합이 허용되며 모두 서로 호환되지 않습니다.

마스터/슬레이브 쌍은 동일한 파라미터 쌍 값을 사용하여 통신해야 합니다. 서로 다른 구성으로 고정된 여러 슬레이브를 사용하는 경우 마스터는 다른 슬레이브와 통신해야 할 때마다 자체적으로 다시 구성해야 합니다.

- CPOL은 전송이 시작될 때 클럭이 하이 또는 로우로 시작되는지 여부를 제어합니다. CPOL = 0이면 클럭이 로우로 시작되고 상승 에지는 SS 라인이 설정된 후 클럭의 첫 번째 에지입니다. CPOL = 1이면 클럭이 하이로 시작되고 하강 에지가 전송의 첫 번째 에지입니다.

- CPHA는 디바이스가 클럭의 첫 번째 에지 또는 두 번째 에지에 있는 MOSI 및 MISO 라인에서 데이터 샘플을 가져올지 여부를 제어합니다. CPHA = 0은 첫 번째 가장자리를 의미하고 CPHA = 1은 두 번째 가장자리를 의미합니다. 상승 또는 하강하는 첫 번째 가장자리는 CPOL 매개변수에 따라 다릅니다.

그림 4: 이 그림은 CPOL 및 CPHA의 네 가지 조합과 SCLK 라인의 극성과 디바이스가 MISO 및 MOSI 라인을 샘플링하는 에지에 미치는 영향을 보여줍니다.

SPI 타이밍 고려 사항

SPI를 사용하여 통신할 수 있는 모든 하드웨어 장치에는 각 신호의 속도, 설정 및 유지 시간에 대한 허용 오차를 제공하는 타이밍 경계가 있습니다. 일반적인 장치에는 아래 이미지의 예와 같이 지정된 중요한 신호가 있습니다.

그림 5: 이 그림은 일반적으로 데이터 시트에 지정된 허용 오차를 갖는 다양한 신호 타이밍 특성을 보여줍니다.

그림 6: 이 표는 클럭 속도, 설정 및 대기 시간에 대한 Min 및 Max 시간에 대한 하드웨어 사양의 예입니다.

SPI의 강점과 약점

강점

- 광범위한 지원 및 IP 사용 가능

- 전이중 통신

- I²C 또는 SMBus보다 높은 처리량

- 전송된 비트에 대한 완벽한 프로토콜 유연성(즉, 8비트 단어로 제한되지 않음)

- 구현하고 이해하는 간단한 프로토콜

- 일반적으로 외부 회로가 필요하지 않음(풀업 저항이 필요한 I²C와 달리)

- 마스터에 의해 클럭되는 시스템은 정밀 발진기 및 PLL이 필요하지 않음을 의미합니다.

- 주소 지정 불필요(복잡성을 줄이고 각 통신에 대한 주소를 보내지 않아 처리량에 도움이 됨)

- 트랜시버가 필요하지 않습니다.

- 직렬 프로토콜은 병렬 인터페이스보다 물리적 연결을 적게 사용합니다.

- 여러 장치에 대한 대부분 공유 회선(각 장치에 대한 별도의 SS 회선 제외)

약점

- SPI를 공식 프로토콜로 관리하는 표준 기관이 없으므로 공급업체별 구현 불일치가 발생합니다.

- 장치가 많을수록 더 많은 핀과 연결이 필요합니다.

- 하드웨어 흐름 제어 없음

- 하드웨어 슬레이브 승인 없음(마스터가 아무 것도 "말"하지 않고 모를 수 있음)

- 다중 마스터 아키텍처를 지원하지 않습니다.

- 비교적 짧은 거리만 처리(일반적으로 온PCB 통신용)

'프로그래밍 > 랩뷰 기술자료' 카테고리의 다른 글

| 랩뷰를 이용한 여러 CPU 병렬 실행 (0) | 2023.03.28 |

|---|---|

| 랩뷰 Loop별 CPU 할당하여 멀티스레딩 구현 (0) | 2023.03.28 |

| 랩뷰 VI 실행 속도 향상방법 (0) | 2023.03.26 |

| 랩뷰 VI 메모리 활용 (0) | 2023.03.26 |

| DAQ장치의 인터페이스 선정 가이드 (0) | 2023.02.17 |