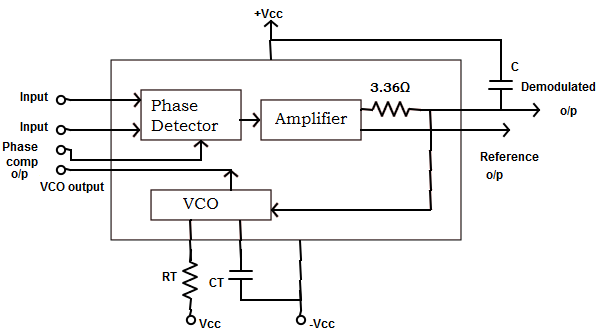

위상 고정 루프는 두 신호의 위상 차이를 비교하여 발진기 회로의 입력 주파수와 출력 주파수 간의 동기화를 유지하는 데 사용되는 회로입니다. 위상 고정 루프는 PLL로 약칭되며 기본적으로 위상 검출기(또는 비교기), 저역 통과 필터 및 전압 제어 발진기와 증폭기로 구성된 피드백 회로입니다.

다양한 응용 분야가 PLL과 관련되어 있지만 PLL 회로의 주요 응용 분야 중 하나는 신호의 일관된 감지입니다. 이는 PLL이 변조 시 발생하는 위상 오류를 제거하는 데 사용되기 때문입니다. 위상 오류는 일반적으로 변조 시점의 반송파 신호와 관련이 있습니다. 따라서 반송파 신호에 메시지 신호를 곱하면 수신단에서 왜곡된 신호가 발생합니다.

따라서 수신기 회로는 위상 고정 루프를 사용하여 신호와 관련된 위상 오류를 제거합니다.

위상 고정 루프(Phase-Locked Loop - PLL)는 전자 시스템의 기본 블록 중 하나입니다. 일반적으로 멀티미디어, 통신 및 기타 여러 응용 프로그램에서 사용됩니다. PLL에는 선형 및 비선형의 두 가지 유형이 있습니다. 비선형은 현실 세계에서 설계하기 어렵고 복잡하지만 선형 제어 이론은 아날로그 PLL에서 잘 모델링되었습니다. PLL은 선형 모델이 대부분의 전자 응용 분야에 충분하다는 것을 입증했습니다.

1. 위상고정루프란?

위상 고정 루프(PLL)의 기본 형태는 전압 제어 발진기(VCO), 위상 검출기(PD) 및 필터로 구성됩니다. 보다 일반적인 형태에서 PLL에는 믹서와 디지털 분배기가 포함될 수도 있습니다. 정상 상태에서 VCO의 주파수는 다음과 같은 표현식으로 제공됩니다.

fo = fm + Nfr

위상 고정 루프(PLL)는 입력 신호의 주파수와 일치하도록 지속적으로 조정되는 전압 또는 전압 구동 발진기가 있는 전자 회로입니다. PLL은 데이터가 중단된 "잡음이 많은" 통신 채널에서 신호를 생성, 안정화, 변조, 복조, 필터링 또는 복구하는 데 사용됩니다.

PLL은 Wi-Fi 라우터, 방송 라디오, 워키토키 라디오, 텔레비전 및 휴대폰을 포함한 무선 또는 무선 주파수(RF) 애플리케이션에 널리 사용됩니다.

간단히 말해서 위상 고정 루프는 주파수 및 위상에 모두 민감한 폐쇄 루프 피드백 제어 회로입니다. PLL은 단일 구성 요소가 아니라 아날로그 및 디지털 구성 요소로 구성된 시스템으로, "네거티브 피드백" 구성으로 상호 연결되어 있습니다. 정교한 연산 증폭기(op amp) 기반 증폭기 회로와 유사하다고 생각하면 됩니다.

PLL은 세 가지 주요 구성 요소로 구성됩니다.

- 위상 검출기(위상 비교기 또는 믹서라고도 함). 두 신호의 위상을 비교하고 위상차에 따라 전압을 생성합니다. 이는 기준 입력과 전압 제어 발진기 출력을 곱합니다.

- 전압 제어 발진기. 주파수가 저역 통과 필터에서 제공하는 중심 주파수와 밀접하게 일치하는 정현파 신호를 생성합니다.

- 저역 통과 필터. 입력 신호의 고주파 교류(AC) 구성 요소를 감쇠하여 신호를 평활화하고 평평하게 하여 DC와 비슷하게 만드는 일종의 루프 필터입니다.

.

2. 위상고정루프 동작원리

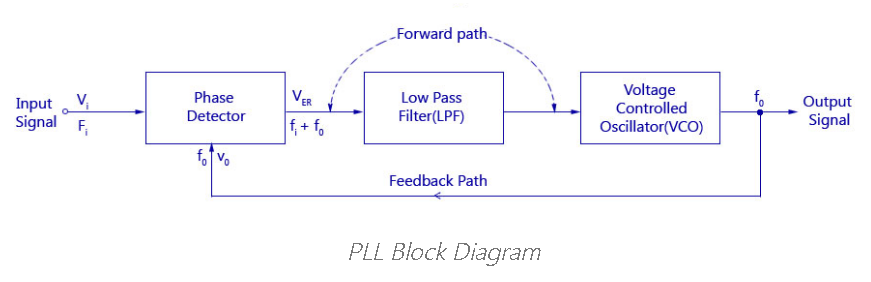

PLL을 사용하면 안정적인 저주파 레퍼런스를 기반으로 고주파 신호를 생성할 수 있습니다. 아래 그림은 일반적인 PLL 블록 다이어그램을 보여줍니다. 안정적인 저주파 레퍼런스 신호는 전압 제어 발진기(VCO)를 구동하여 레퍼런스 주파수의 N배의 신호를 출력합니다. 기본 PLL에서 N은 정수이지만 고급 회로를 사용하면 N을 정수가 아닌 것으로 만들 수 있습니다. 이러한 유형의 설계를 fractional-N 합성이라고 합니다.

주파수 분배기는 출력을 N의 계수만큼 하향 변환한 다음 위상 검출기가 기준 신호와 하향 변환된 출력 간의 위상차를 측정합니다. 두 신호의 주파수가 같으면 위상차는 일정합니다. 여기에서 "위상 고정"이라는 용어가 유래했으며, 두 신호는 두 신호 사이에 일정한 위상차와 함께 잠겨 있습니다.

위상 고정 루프는 위상 검출기, 전압 제어 발진기로 구성되며 그 사이에는 저역 통과 필터가 고정되어 있습니다. 입력 주파수가 'Fi'인 입력 신호 'Vi'는 위상 검출기에 의해 인정됩니다. 기본적으로 위상 검출기는 피드백 주파수 fo를 통해 입력 주파수 fi를 비교하는 비교기입니다.

위상 검출기의 출력은 DC 전압인 (fi+fo)입니다. 위상 검출기로부터, 즉 DC 전압은 저역 통과 필터(LPF)에 입력됩니다. 고주파 노이즈를 제거하고 안정적인 DC 레벨, 즉 Fi-Fo를 생성합니다. Vf는 PLL의 동적 특성이기도 합니다.

저역 통과 필터의 출력, 즉 DC 레벨은 VCO로 전달됩니다. 입력 신호는 VCO(fo)의 출력 주파수에 정비례한다. 입력 및 출력 주파수는 출력 주파수가 입력 주파수와 같아질 때까지 피드백 루프를 통해 비교되고 조정됩니다. 따라서 PLL은 자유 실행, 캡처 및 위상 잠금처럼 작동합니다.

입력 전압이 인가되지 않으면 자유 주행 단계라고 합니다. VOC에 적용된 입력 주파수가 변경되어 비교를 위한 출력 주파수를 생성하는 즉시 이를 캡처 단계라고 합니다.

3. 위상 고정 루프 감지기

위상 고정 루프 검출기는 VCO의 입력 주파수와 출력 주파수를 비교하여 두 주파수의 위상 차이에 정비례하는 DC 전압을 생성합니다. 아날로그 및 디지털 신호는 위상 고정 루프에서 사용됩니다. 대부분의 모놀리식 PLL 집적 회로는 아날로그 위상 검출기를 사용하며 대부분의 위상 검출기는 디지털 유형입니다. 이중 평형 혼합 회로는 아날로그 위상 검출기에 일반적으로 사용됩니다. 몇 가지 일반적인 위상 검출기는 다음과 같습니다.

1) 익스클루시브 OR 위상 검출기

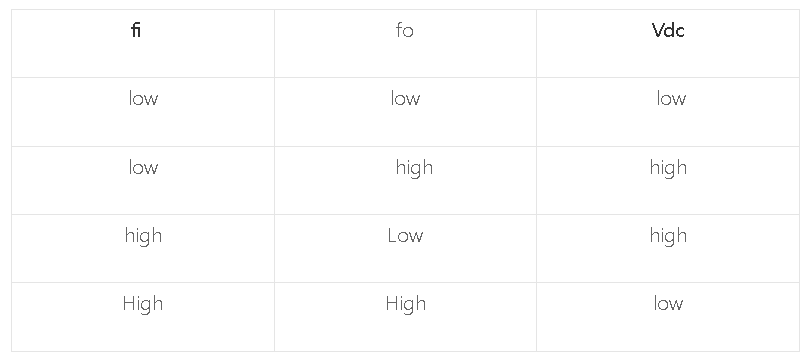

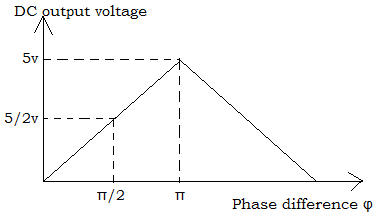

전용 OR 위상 검출기는 CMOS IC 4070 유형입니다. 입력 및 출력 주파수는 EX OR 위상 검출기에 적용됩니다. 출력을 높게 얻으려면 적어도 하나의 입력이 낮아야 하고 출력의 다른 조건이 낮아야 하며. 파형, 입력 및 출력 주파수, 즉 fi와 fo의 위상차가 0도라고 가정하면 비교기의 DC 출력 전압은 두 입력 간의 위상차의 함수가 됩니다.

fi와 fo 사이의 위상차의 기능은 DC 출력 전압 그래프와 같습니다. 위상 검출기가 180도이면 출력 전압이 최대입니다. 입력 및 출력 주파수가 모두 구형파인 경우 이러한 유형의 위상 검출기가 사용됩니다.

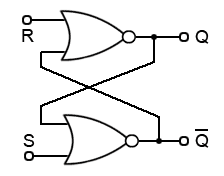

2) 엣지 트리거 위상 검출기

에지 트리거 위상 검출기는 입력 및 출력 주파수가 듀티 사이클이 50% 미만인 펄스 파형에 있을 때 사용됩니다. R-S 플립 플롭은 아래 그림과 같은 위상 검출기에 사용됩니다. R-S 플립플롭에서, 두 개의 NOR 게이트는 교차 결합됩니다.

phase detector 의 output 는 R-S flip flop 를 트리거하여 logic state 를 변경할 수 있습니다. 입력 및 출력 주파수의 양극 가장자리는 위상 검출기의 출력을 변경할 수 있습니다.

3) 모놀리식 위상 검출기

모놀리식 위상 검출기는 CMOS 유형, 즉 IC 4044입니다. 고조파 감도로부터 크게 보상되며 회로가 입력 신호의 전환에만 응답할 수 있기 때문에 듀티 사이클 문제가 버려집니다. 중요한 응용 분야에서는 가장 열이 많이 나는 위상 검출기입니다. 진폭의 독립적인 변동은 입력 파형의 위상 오류, 출력 오류 전압 및 듀티 사이클로부터 자유롭습니다.

'데이터계측분석 > 전기전자 기술자료' 카테고리의 다른 글

| OLED 기술의 종류와 동작방식 (0) | 2024.09.20 |

|---|---|

| 반파정류기의 이해 (0) | 2024.09.20 |

| 바이패스 커패시터의 이해 (0) | 2024.09.17 |

| LM723 전압 조정기 (0) | 2024.09.16 |

| LM7912 네거티브 전압 레귤레이터 (1) | 2024.09.16 |