로직 게이트란?

논리 게이트는 논리 연산을 수행하여 Boolean 함수를 구현하는 데 사용됩니다. 바이너리 로직을 입력으로 사용하고 바이너리 로직을 출력으로 생성합니다.

논리 게이트는 기본적으로 디지털 회로의 빌딩 블록입니다. 세계의 모든 디지털 시스템은 논리 게이트로 구성되어 있습니다.

논리 게이트는 이진 논리에서 작동하며 High-State "1" 및 Low-State "0"을 참조합니다.

기본 및 파생 논리 게이트

AND, OR, NOT, NAND는 기본 논리 게이트가 아닙니다. 기본 게이트는 함께 결합되어 XOR, XNOR 등과 같은 파생 논리 게이트를 형성합니다.

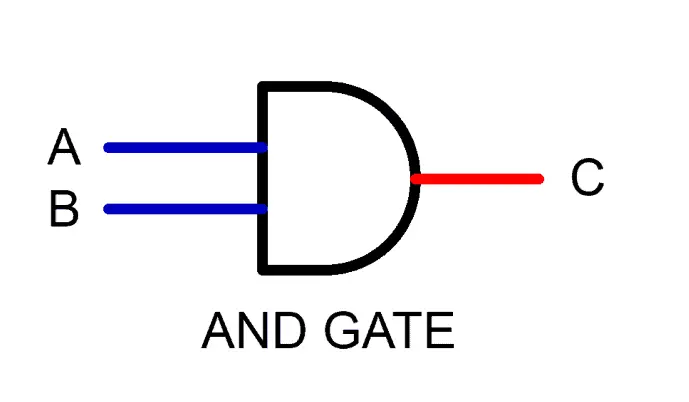

로직 AND 게이트란?

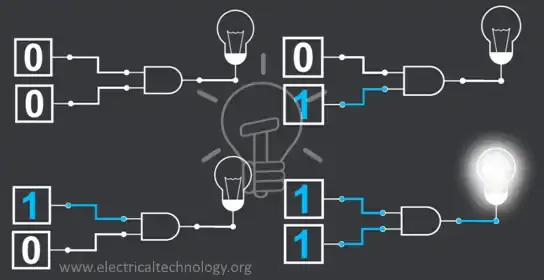

AND 게이트는 AND 게이트에 대한 모든 입력이 High-State "1"인 경우 High-State "1"을 제공하는 기본 논리 게이트입니다. 입력 중 하나라도 Low-State "0"이면 출력은 Low-State "0"입니다. 산술 곱셈 연산이라고도 합니다.

AND 게이트 로직 심볼, 부울 표현식 및 진리표

AND 게이트 기호전 세계적으로 AND 게이트에 사용되는 기호에는 3가지 유형이 있습니다.

미국 국립 표준 협회 (ANSI) / 군사

국제전기기술위원회(IEC)/유럽

Deutsches Institut für Normung (DIN)/독일

C = A.B or C = A & B

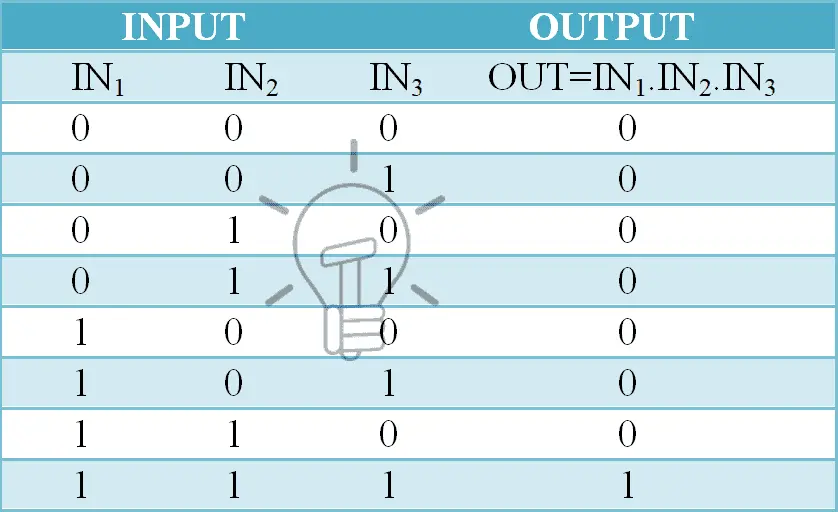

디지털 회로의 입력-출력 로직 조합을 지정하는 데 사용되는 수학 테이블을 진리표라고 하며, AND 게이트의 진리표는 다음과 같습니다.

AND 게이트 로직 플로우 개략도

AND 게이트의 건설 및 작동 메커니즘 :

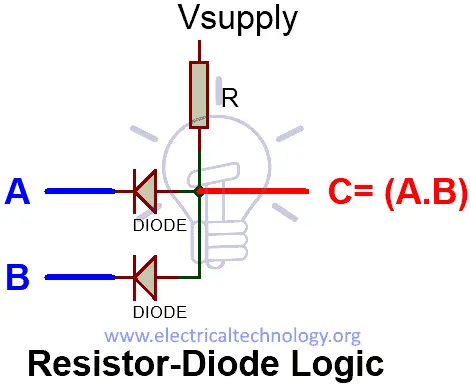

RDL(Resistor-Diode Logic)을 사용하는 AND 게이트

RDL(Resistor-Diode Logic)에서 다이오드는 스위치로 사용됩니다. AND 게이트에서 다이오드는 두 입력 중 하나가 로직 로우 "0"일 때 이러한 구성에 배치되며, 해당 다이오드는 순방향 바이어스가 되고 경로에 저항이 없기 때문에 로직 로우"0"이 출력을 통해 흐릅니다. 두 입력이 모두 로직 하이인 경우 "1" 다이오드는 역방향 바이어스되므로 Vsupply(로직 하이 상태)는 출력 C에 "1"로 라우팅됩니다.

실리콘의 경우 약 0.7V, 게르마늄 다이오드의 경우 0.3V의 다이오드 순방향 전압 강하가 항상 있습니다.

RTL(Resistor-Transistor Logic)을 사용하는 AND 게이트

RTL(Resistor-Transistor Logic)에서 주 스위칭 장치는 트랜지스터입니다. 아래 그림에는 로직 레벨 높은 "2"로 켜지는 1개의 NPN 트랜지스터가 직렬로 연결되어 있으며, 두 트랜지스터가 모두 켜지면 Vcc"1"이 출력을 통해 흐릅니다. 출력에 연결된 풀다운 저항이 있으므로 두 트랜지스터가 모두 켜지지 않는 한 출력에 항상 Logic-Low"0"이 있습니다.

알림: RTL 로직 제한 또는 단점은 BJT가 켜져 있을 때 기본 저항과 컬렉터 저항의 전류 흐름으로 인해 전력 손실이 높다는 것입니다.

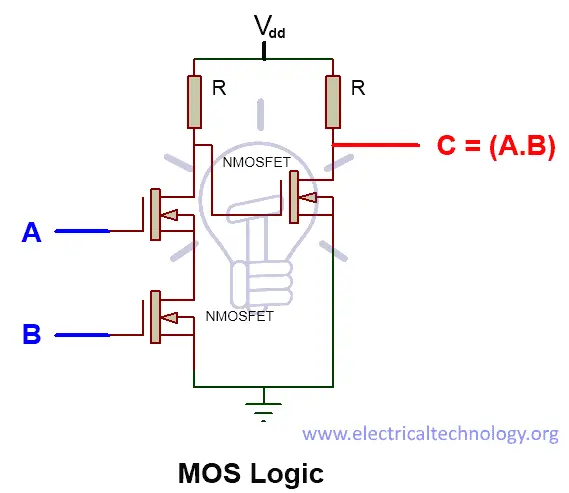

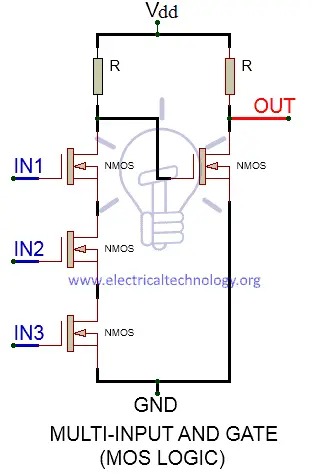

MOS Logic을 사용한 AND 게이트

MOS Logic에서는 MOSFET이 메인 스위칭 유닛으로 사용됩니다. 아래 그림에서 볼 수 있듯이 직렬로 연결된 두 개의 MOSFET은 입력 신호에 의해 제어되고 있으며, 차례로 이러한 NMOSFET은 다른 NMOSFET을 제어합니다. 두 입력이 모두 High-State"1"이면 직렬로 연결된 NMOS가 활성화되고 연속적으로 OUTPUT 측의 NMOS가 로직 로우 게이트 입력(GND)으로 인해 꺼집니다. 따라서 출력에 대한 유일한 경로는 Vdd(로직 하이)입니다.

이 입력 중 하나라도 Low-State"0"이면 직렬로 연결된 NMOS가 꺼지고 OUTPUT 측(Switched-on)의 NMOS 게이트에서 High State"1"이 됩니다. NMOS가 켜지면 출력 C가 GND(Low State"0")에 직접 연결됩니다.

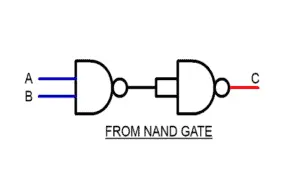

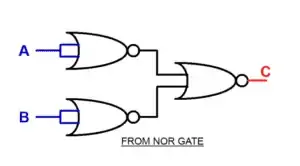

AND 다른 논리 게이트의 게이트

그리고 게이트의 기능은 서로 다른 논리 게이트의 다양한 조합에 의해 달성 될 수 있으며, 그 중 일부는 아래에 나와 있습니다.

부울 표현 :

C = ((A.B)')'

C = AB

C = (A'+B')'

C = (a'+b')'

C = ((A+A)' + (B+B)')'

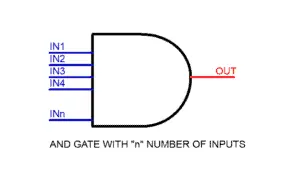

다중 입력 AND 게이트

이전에 설정했듯이 AND 게이트는 논리 High State"1"만 제공하고 모든 입력이 논리 High State"1"인 경우에만 제공합니다. 입력 진리표의 "n"수는 다음과 같습니다.

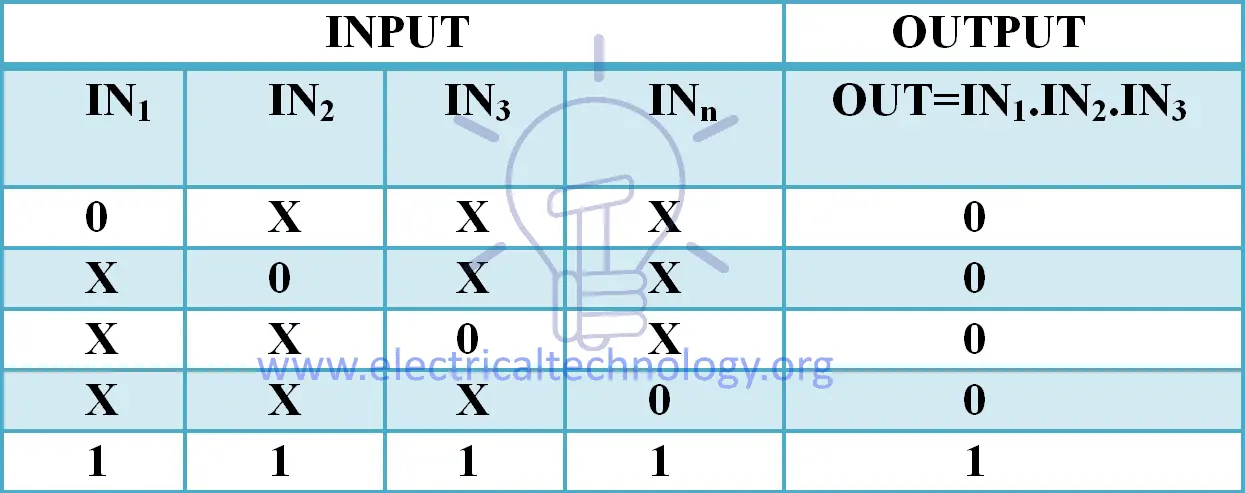

진리표

아래 표에서 "X"는 "상관없음"을 의미합니다. "1"일 수 있고 "0"이 될 수 있습니다. 즉, "0"을 전달하는 단일 입력이 있는 한 출력은 항상 "0"이므로 다른 입력을 확인할 이유가 없으므로 "X를 신경 쓰지 않음"이라고 합니다.

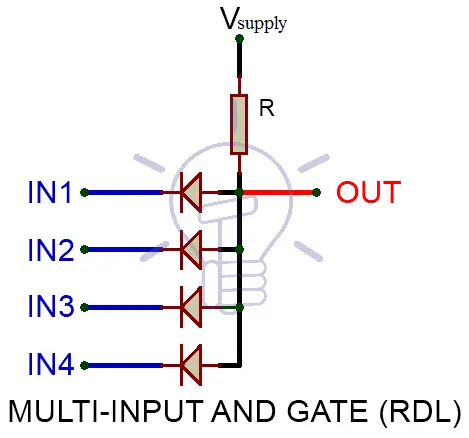

저항기-다이오드 로직

RDL(Resistor-Diode logic) 로직에서는 모든 입력 라인에 다이오드가 사용되므로 다이오드를 추가하면 아래 그림과 같이 입력 라인 수가 증가할 수 있습니다. 각 입력은 별도의 다이오드에 공급됩니다. 원하는만큼 다이오드를 배치하여 Multi-Input AND GATE를 만듭니다.

저항기-트랜지스터 로직

RTL(Resistor-Transistor Logic)에서 트랜지스터는 스위칭 장치로 사용됩니다. 입력 라인을 늘리려면 아래 그림과 같이 직렬로 연결된 트랜지스터의 수를 늘려야 합니다.

MOS 로직

MOS 로직의 경우는 RTL 로직과 동일하지만, 대신 입력측에서 직렬로 연결된 MOSFET의 수를 늘립니다. 그리고 MOS 로직에 3개의 입력이 있는 GATE는 다음과 같습니다. 다른 입력을 추가하려면 직렬로 다른 NMOS를 추가하십시오.

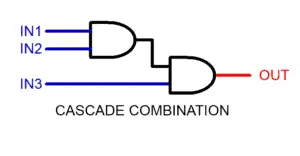

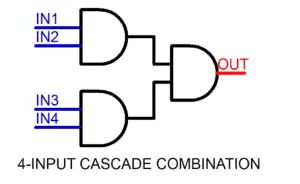

AND 게이트의 계단식 설정

다중 입력 AND 게이트 기능은 아래에 주어진 특정 구성에서 Two-Input AND 게이트를 캐스케이딩하여 달성할 수 있습니다

OUT = IN1 & IN2 & IN3

OUT = (IN1 & IN2) & IN3

OUT = IN1 & IN2 & IN3 & IN4

OUT = (IN1 & IN2) & (IN3 & IN4)

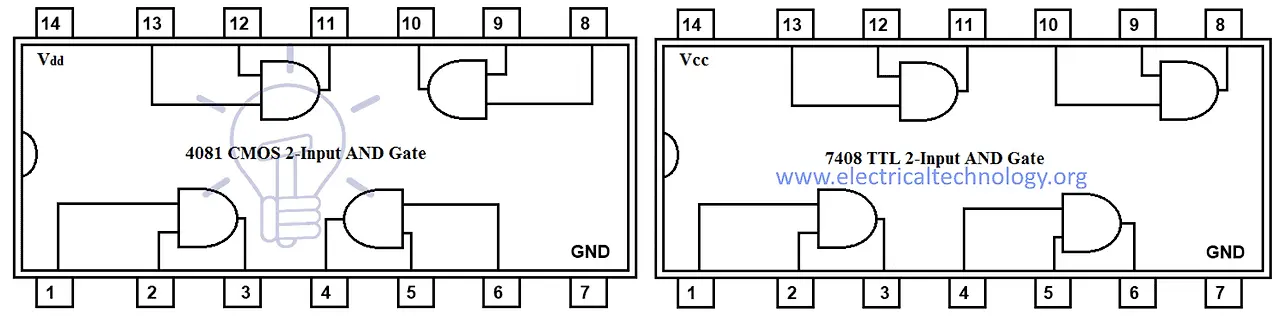

TTL 및 CMOS 로직 및 게이트 IC

상업적으로 최대 4개의 입력 AND 게이트 IC가 시중에서 판매되고 있으며, 단일 패키지에 2개의 AND 게이트가 있습니다. 핀 세부 정보가 있는 일부 IC는 다음과 같습니다.

TTL 로직 및 게이트

- 74LS08 쿼드 2입력

- 74LS11 트리플 3입력

- 74LS21 듀얼 4입력

CMOS 로직 및 게이트

- CD4081 쿼드 2입력

- CD4073 트리플 3입력

- CD4082 듀얼 4 입력

7408 TTL 및 4081 CMOS 및 게이트 IC(2입력)

7408 TTL 및 게이트 IC용 핀아웃

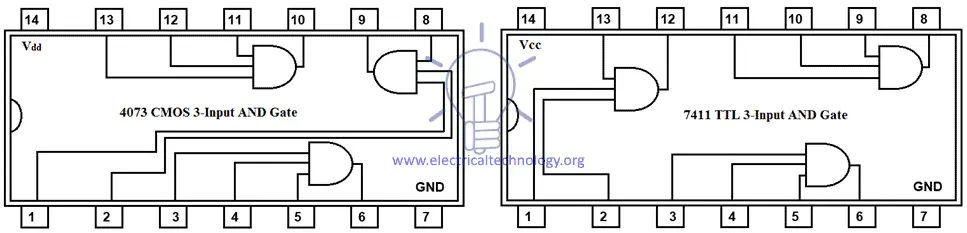

4073 CMOS 및 7411 TTL 및 게이트 IC(3 입력)

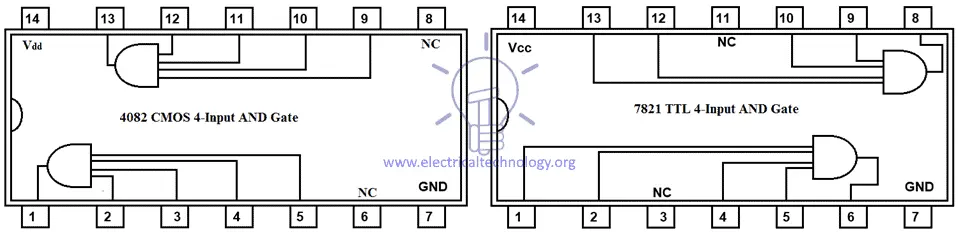

4082 CMOS 및 7821 TTL 및 게이트 IC(4 입력)

'데이터계측분석 > 전기전자 기술자료' 카테고리의 다른 글

| ELCB (누전 회로 차단기) (0) | 2023.09.10 |

|---|---|

| 배터리 및 셀의 종류와 응용 분야 (0) | 2023.09.09 |

| RS232통신 - MAX232 구성, 동작, 유형 (0) | 2023.09.08 |

| AWG 와이어 게이지 및 전류용량 (0) | 2023.09.08 |

| 전기 접지 – 접지 방법 및 유형 (0) | 2023.09.08 |