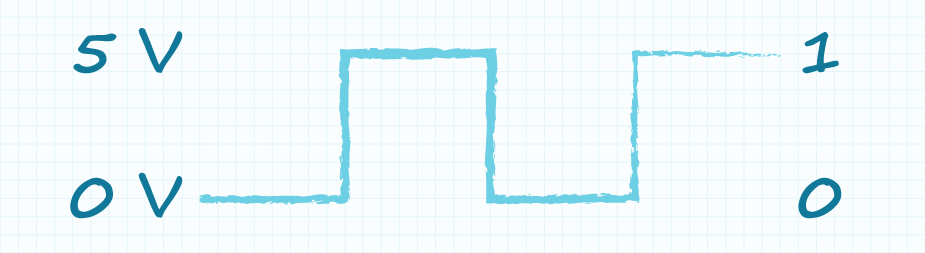

풀다운 저항은 디지털 장치의 핀과 접지 사이에 연결됩니다. 전압을 로직 로우 레벨로 낮춥니다.풀다운 저항은 디지털 신호 처리의 안정성과 신뢰성을 보장하며 다양한 디지털 전자 회로 및 집적 회로의 필수 구성 요소입니다.풀다운 저항 회로의 구성과 동작방식에 대해 알아보겠습니다. 1. 풀다운 저항이란?디지털 전자 회로에서 풀다운 저항은 회로의 안정성을 보장하기 위해 접지와 신호 라인 사이에 연결된 수동 회로 요소입니다.따라서 풀다운 저항은 활성 구동 신호가 없는 경우 신호 라인을 명확한 논리 레벨(일반적으로 0 또는 낮은 전압 레벨)에 연결합니다. 이 저항은 풀업 저항과 동일한 기능을 수행하며, 즉, 신호 라인의 부동 상태를 방지하여 회로에 신뢰성과 안정성을 제공합니다. 5V에서 작동하는 디지털 회로..